# New Power Stage Building Blocks for Small Motor Drives

Eric R. Motto\*, John F. Donlon\*, H. Iwamoto\*\*

\* Powerex Inc., Youngwood, Pennsylvania, USA

\*\* Mitsubishi Electric, Power Device Division, Fukuoka, Japan

#### Abstract:

This paper will present two newly developed hybrid power modules designed for low cost, compact, motor drives. The first, is a miniaturized version of the transfer molded DIP-IPM which has been previously presented [6][7]. It will be shown that this new device offers significant size and manufacturability advantages compared to discrete approaches using TO-220 copackaged IGBTs.

The second, is a module intended to simplify small motor drives employing Pulse Amplitude Modulation (PAM). It will be shown that increased system efficiency, high input power factor, and reduced harmonics are achieved through the use of an optimized trench gate IGBT with a custom control IC to provide boost type power factor correction.

#### I. THE DIP-IPM

Historically, small motor drives for consumer appliance applications have relied mainly on discrete copackaged (containing both IGBT and free wheel diode) devices in TO-220 or TO-247 packages. The main drawback of this approach is its cumbersome assembly that requires mounting and isolating multiple packages. Previously, an isolated, transfer molded, hybrid device called DIP-IPM was proposed [11][12] as a new approach for these applications. The DIP-IPM series is designed for basic

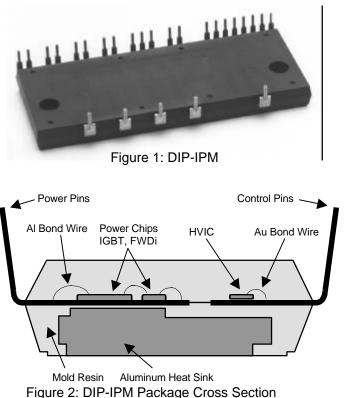

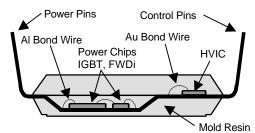

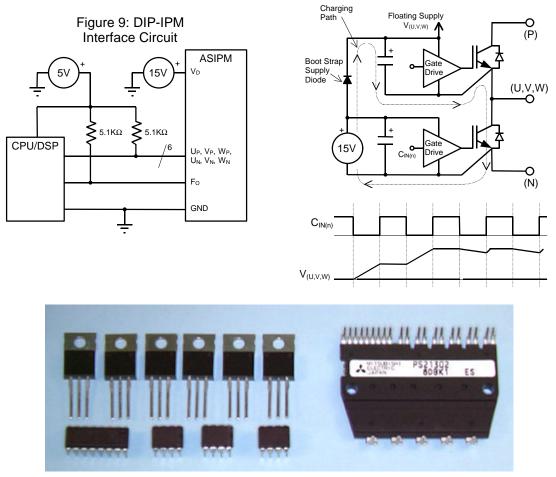

speed control in consumer appliance applications. In these applications, a small, low-cost and efficient power stage that can be easily integrated into the finished equipment is required. In order to achieve these targets, a new transfer molded package was developed. A photograph of the DIP-IPM is shown in Figure 1 and a cross section diagram is shown in Figure 2. Low cost is achieved by assembling bare power chips along with custom HVIC and LVIC die on a lead frame like a giant integrated circuit. The lead frame assembly is molded in epoxy resin along with an aluminum heat sink to provide good thermal characteristics. This process reduces cost and manufacturing time by eliminating the need for separate packaging of the power devices and control ICs. In addition, the relatively expensive IMS (Insulated Metal Substrate) or ceramic substrate that is used in conventional hybrid modules is not required. The transfer molded package is also well suited for high volume, low cost mass production. The DIP-IPM is effective in terms of size and cost for applications that would normally utilize TO-247 type discrete devices. Unfortunately, the DIP-IPM is often too large and expensive for lower power applications that can utilize TO-220 devices.

Figure 5: Mini DIP-IPM Block Diagram

## **II. THE MINI DIP-IPM**

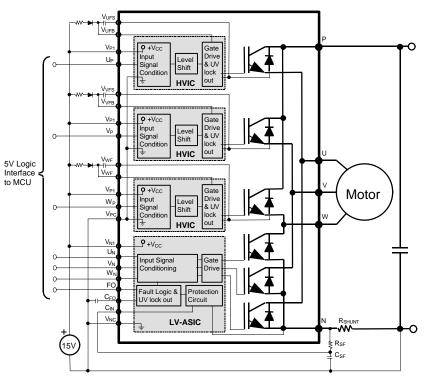

The Mini DIP-IPM was developed to provide the low cost and smaller size required in lower power applications. Figure 3 is a photograph comparing the DIP-IPM and the new Mini DIP-IPM to a TO-220 discrete device. Like the larger DIP-IPM the new DIP-IPM Mini contains six IGBT/free wheel diode pairs along with the HVICs (High Voltage Integrated Circuits) required for a three phase motor drive application. Figure 4 shows a cross section of the new single step transfer molded package. This new isolated package is lower cost and more easily manufactured than the DIP-IPM. A block diagram of the Mini DIP-IPM is shown in Figure 5. The input voltage for the target applications is generally between

100VAC and 240VAC. To cover this range, IGBTs and free wheel diodes with a 600V  $V_{CES}$  rating were selected. Most of the target applications are powered from a single phase AC source but flexibility to accommodate three phase sources, active power factor correction and voltage doubler (Figure 6) topologies is desired. Due to these requirements and the limited capabilities of the lead frame design, it was determined that the rectifier converter should not be integrated in the Mini DIP-IPM. The IGBT inverter section is a standard three phase bridge containing six IGBT+FWDi pairs. For optimum system cost, the decision was made to develop two different types of IGBT chips. High speed chips are used when the application requires switching frequencies greater than 5kHz and low speed (low saturation voltage) chips are used when the required switching frequency is less than 5kHz. At this writing, there are three Mini DIP-IPMs in production and several additional types under development. Table 1 shows the typical application and type names of the DIP-IPM and Mini-DIP devices.

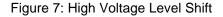

Figure 5 is a block diagram showing the Mini DIP-IPM's integrated control and protection functions along with some of the

required external support circuitry. The input signal level shifting function and under voltage protection for the p-side IGBT chips is accomplished using three custom HVICs. Over current protection and n-side drive under voltage protection for the three low side IGBTs is provided by a custom low voltage ASIC.

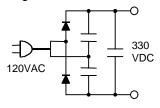

The Mini DIP-IPMs built-in level shift eliminates the need for opto-couplers and allows direct connection of all six control inputs to the CPU/DSP. The detailed operation and timing diagram for the level shift function is shown in Figure 7. The falling and rising edges of the p-side

control signal (A) activate the one shot pulse logic which generates turn on pulses (B, C) for the high voltage MOSFETs. Narrow on pulses are used to minimize the power dissipation within the HVIC. The high voltage MOSFETs pull the inputs to the high side driver latch (D, E) low to set and reset the gate drive for the p-side IGBT (F).

Power for the high side gate drive is normally supplied using external boot strap circuits as shown in Figure 5. The operation of the boot strap is outlined in Figure 8. When the low side IGBT is turned on, the floating supply capacitor is charged through the boot strap diode. When the n-side IGBT is off, the energy stored in the capacitor provides power for the high side gate drive. Using this technique it is possible to operate all six IGBT gate drivers from a single 15V supply. The boot strap circuit is a very cost effective method for providing power for the high side IGBT gate drive. However, care must be exercised to maintain the high side supplies when the inverter is idle and during fault handling conditions. This usually means that the low side IGBTs must be pulsed on periodically even when the inverter is not running. At power up, the boot strap supplies

| Table 1: DIP-IPMs               |                               |            |            |             |

|---------------------------------|-------------------------------|------------|------------|-------------|

| DIP-IPM                         | Inverter Rating (IGBT rating) |            |            |             |

| Line-up                         | 200W (5A)                     | 400W (10A) | 750W (15A) | 1500W (20A) |

| Low<br>Frequency<br>Type <5KHz  | PS21202                       | PS21213    | PS21204    | PS21205     |

| High<br>Frequency<br>Type >5KHz | PS21212                       | PS21213    | PS21214    |             |

| Mini DIP-IPM<br>Line-up         |                               |            |            |             |

| Low<br>Frequency<br>Type <5KHz  | PS21342                       |            |            |             |

| High<br>Frequency<br>Type >5KHz | PS21352                       | PS21353    |            |             |

must be charged before the PWM is started. Normally, this is accomplished by a burst of pulses on the low side IGBTs.

The Mini DIP-IPM is protected from failure of the 15V control power supply by a built in under voltage lock out circuit. If the voltage of the control supply falls below the UV level specified on the data sheet, the low side IGBTs are turned off and a fault signal is asserted. In addition, the p-side gate drive circuits have independent under voltage lock out circuits to protect against failure of the boot-strap power supplies.

The Mini DIP-IPM uses the voltage across an external shunt resistor inserted in the negative DC bus to monitor the current and provide protection against overload and short circuits. An RC filter with a time constant of 1.5 to  $2\mu$ s is inserted as shown in Figure 5 to prevent erroneous fault detection due to di/dt induced noise at switching events. When the voltage at the CIN pin exceeds the V<sub>SC</sub> reference level

Figure 8: Boot Strap Supply Operation

Figure 10: Mini DIP-IPM Comparison to Discrete Solution

specified on the device data sheet the lower arm IGBTs are turned off and a fault signal is asserted at the FO output. The IGBTs remain off until the fault time ( $t_{FO}$ ) has expired and the input signal has cycled to its off state. The duration of  $t_{FO}$  is set by an external capacitor  $C_{FO}$ .

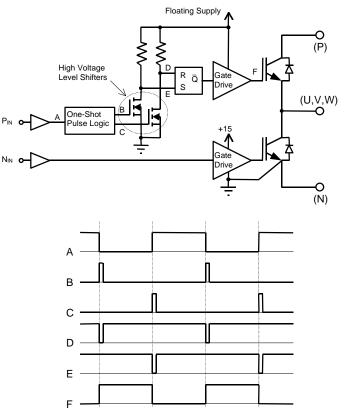

The Mini DIP-IPM has seven microprocessor compatible input and output signals. All signals are 5V TTL/CMOS compatible and referenced to the common ground of the control power supply allowing direct connection to the MCU. Figure 9 shows a typical external interface circuit. On and off operations for all six IGBTs in the ASIPM are controlled by the active low control inputs. Normally, these inputs are pulled high to the 5V logic supply of the MCU with an external resistor. The MCU commands the IGBT to turn on by pulling the respective input low. Hysteresis is provided on all inputs to prevent oscillations and enhance noise immunity. The fault signal output is in an open collector configuration. When a fault occurs the ASIPM pulls the fault line low.

Figure 10 clearly shows that the Mini DIP-IPM has an advantage in terms of size and component count over a typical discrete approach. The reduced manufacturing time and simplified assembly provided by the Mini DIP-IPM will allow improvements in both cost and reliability of the finished system.

## **III. THE AFIPM**

As small motor drives are implemented in an ever increasing array of applications, power system "pollution" caused by the poor power factor and high harmonic content characteristic of the rectifiercapacitor input sections can present serious problems. As a result, a number of international Figure 11: AFIPM Block Diagram

AFIPM

organizations have developed standards that place limits on this "pollution". One way to solve these problems is to adopt an active filter front end. If the filter is implemented using a boost topology, a low harmonic content, high power factor input can be achieved while producing a variable DC link voltage suitable for PAM (Pulse Amplitude Modulation). Compared to classical PWM schemes, PAM is desirable in small motor drives because it allows increased efficiency and better utilization of the power devices. In addition, harmonic induced iron losses in the motor can be reduced. The main drawback of this approach is the added complexity and increased manufacturing costs associated with the active filter. A new hybrid module called AFIPM (Active Filter Intelligent Power Module) has been developed to provide a simplified power factor corrected front end for

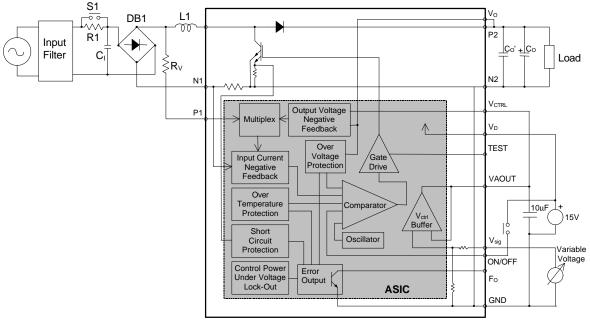

small motor drives and similar applications. As shown in Figure 11, the AFIPM contains all of the power devices and control circuits necessary for the active filter/power factor correction. A photograph of the PM52AUBW060 AFIPM is shown in Figure 12.

# A. AFIPM Application Circuit

Figure 11 is a block diagram of the AFIPM along with a typical external circuit. The AC input line is normally filtered as required to meet agency approvals. The output of the line filter is connected to the single phase input rectifier through a soft start circuit consisting of S1 and R1. At initial power up the output capacitor  $C_0$  is charged through R1 which is typically a  $5\Omega$ , 15W resistor. Once  $C_0$  is charged S1 is closed to carry the main load current. In order to remove noise from the input line a high frequency film type capacitor  $C_1$  of about  $3.3\mu$ F is connected as shown in figure 11. The output of the rectifier bridge DB1 is connected to the AFIPM through the main boost inductor L1. With PM52AUBW060 the boost inductor is normally rated 1.0mH, 20A. Input voltage sensing is accomplished by connecting the positive side of DB1 to the P1 input of the AFIPM through a series resistance  $R_V$ . For 240VAC applications  $R_V$  should be 270K $\Omega$  and for 120VAC  $R_V$  is not required. On the output of the AFIPM (P<sub>2</sub> to N<sub>2</sub>) a filter consisting of  $C_0$  and  $C_0$ ' must be connected.  $C_0$ ' should be a high frequency film of about  $3.3\mu$ F at 630V.

$C_0$  should be a high frequency electrolytic in the 1000µF to 1500µF range at 450V. It is very important that  $C_0$  and  $C_0$ ' be connected as close as possible the P<sub>2</sub> and N<sub>2</sub> pins in order to prevent high transient voltage during the switching of the boost IGBT. The output voltage sensing terminal (V<sub>0</sub>) must be connected to P<sub>2</sub> to close the output voltage negative feedback loop. Failure to make this connection will result in excessive voltage that is likely to damage the AFIPM.

## **B. AFIPM Control Interface**

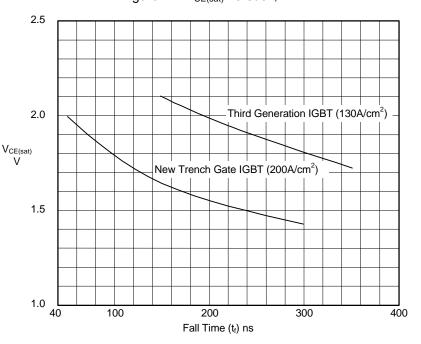

Applying a variable voltage to the Vsig input controls the DC output voltage of the AFIPM. The relationship between  $V_{sig}$  and the AFIPM's output voltage is shown in figure 13. The

Figure 14: V<sub>CE(sat)</sub> versus t<sub>f</sub>

Vsig voltage is buffered by the AFIPM's internal circuit and returned at the VAOUT pin. Normally the voltage at VAOUT is filtered with a  $10\mu$ F capacitor and supplied to the V<sub>ctrl</sub> input of the output voltage negative feedback circuit as shown in Figure 11.

## C. Performance of the AFIPM

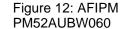

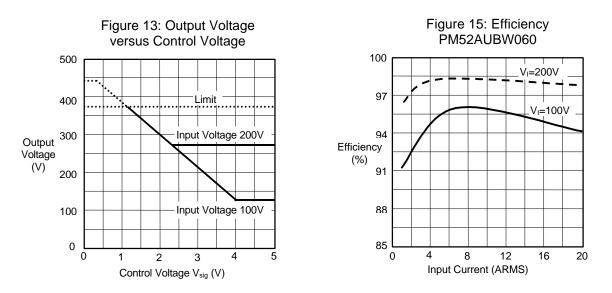

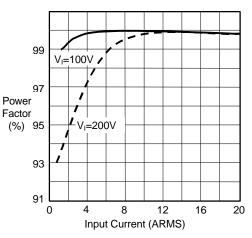

In order to achieve high system efficiency it is necessary to minimize the losses in the active filter. To do this, an optimized trench gate IGBT was developed for the AFIPM. A special IGBT was needed because the AFIPM operates at 20KHz to minimize the input filter requirements. Figure 14 shows the Vce(sat) versus fall time trade off for the optimized 50A 600V trench gate IGBT chip used in the AFIPM. The efficiency of the AFIPM versus input current is shown in figure 15.

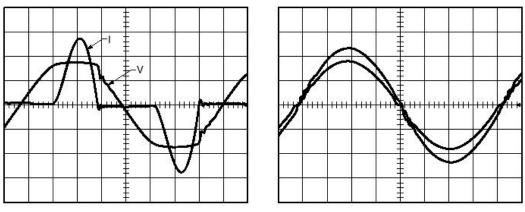

The effect of the AFIPM is easily seen in the input current waveform shown in Figure 16. Figure 17 shows the power factor as a function for load current.

#### AC Input Waveforms without A/F IPM

AC Input Waveform with A/F IPM

Figure 16: AFIPM Oscilloscope Current

# **D. AFIPM Protection Functions**

The AFIPM has built in protection against over voltage, over temperature, short circuit, and control supply failure. The following subsections describe each of these protection functions.

**Output Voltage Overshoot Protection (OV<sub>1</sub>):** A boost type active filter circuit has the unique characteristic the output voltage increases when the load becomes light. In order to prevent this from happening, the IGBT's drive is stopped if the output voltage exceeds the commanded value by more than 20V. Once the voltage returns to the commanded value normal operation of the AFIPM will resume.

**Output Over-Voltage Protection (OV<sub>2</sub>) :** If the output voltage reaches the  $OV_2$  trip level specified on the data sheet the IGBT's gate drive will be cut off and a fault signal will be generated on the FO signal line. In order for normal operation to resume the ON/OFF control signal must be toggled.

Figure 17: Power Factor PM52AUBW060

Short Circuit Protection (SC): If the IGBT's collector current exceeds the SC level specified on the data sheet the gate drive will be cut off and a fault signal will be generated on the FO signal line. In order for normal operation to resume the ON/OFF control signal must be toggled.

**Control Power Supply Under Voltage Lock-Out (UV):** If the control voltage drops below the UV trip level specified on the data sheet the IGBT's gate drive will be cut off and a fault signal will be generated on the FO signal line. Once the supply has exceeded the under voltage reset level  $(UV_r)$  normal operation will resume.

Over Temperature Protection (OT): If the case temperature exceeds the OT level specified on the data sheet the IGBT gate drive is cut off and a fault signal will be generated on the FO signal line. Once the

case temperature drops to the over temperature reset level OT<sub>r</sub> the fault signal clears and normal operation will resume.

## IV. CONCLUSION

This paper has presented two newly developed hybrid power modules. The first, a miniaturized version of the transfer molded DIP-IPM offers significant size and manufacturability advantages compared to discrete approaches using TO-220 copackaged IGBTs.

The second, the AFIPM simplifies the design of boost type active power factor correction for small motor drives employing Pulse Amplitude Modulation (PAM) and similar applications.

#### V. REFERENCES

- [1] G. Majumdar, et al. "A New Generation High Performance Intelligent Module" PCIM Europe May 1992

- [2] Powerex "IGBTMOD and Intellimod<sup>™</sup> Application and Technical Data Book" Second Edition, PUB#9DB-200, 1998

- [3] E. Motto, et. al. "A New Intelligent Power Module With Microprocessor Compatible Analog Current Feedback, Control Input, and Status Output Signals", 1996 IEEE IAS Conference Proceedings

- [4] Eric R. Motto "A New Ultracompact ASIPM with integrated HVASIC" 1997 Powersystems World conference proceedings

- [5] G. Majumdar et. al. "Novel Intelligent Power Modules for Low-Power Inverters" 1998 IEEE PESC Proceedings

- [6] S. Noda et. al. "A Novel Super Compact Intelligent Power Module" 1997 PCIM Europe conference proceedings

- [7] Eric R. Motto "Application Specific Intelligent Power Modules A Novel Approach to System Integration In Low Power Drives" 1998 Powersystems World conference proceedings